Stap 1: 555 Timer Pin Diagram

Fig 1 toont de pin aansluitingen aan de 555 timer, dat het was nemen rechtstreeks vanuit het 555 timer gegevensblad. De stroomaansluitingen naar de chip zijn via pin 1 (grond) en 8 (+ Vcc). De levering van de positieve spanning (+ Vcc) moet tussen 5 en 15V.

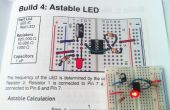

Het tweede beeld is afgesloten van het diagram waarin u ziet de interne functionele onderdelen van de chip. Dit bestaat uit een paar verschillende elementen: weerstanden, transistoren, comparatoren, een flip flop en een output stadium.

Alle drie weerstanden routerplan in fig 2 zijn 5kOhm (zie afbeelding opmerkingen in fig 3). Het doel van deze weerstanden is een voltage scheidingslijn tussen Vcc en grond instellen. Aangezien alle weerstanden dezelfde waarde weten we dat de spanning op de kruising tussen de weerstanden 2/3Vcc en 1/3Vcc (zie afbeelding opmerkingen in Fig. 2). Deze spanningen worden gebruikt als referentie spanning voor de comparatoren.

Een Comparateur is een schakeling die een ingang met een referentie spanning vergelijkt en uitgangen van een laag of hoog signaal, gebaseerd op de input gaat een hogere of lagere spanning dan de verwijzing. De 555 timer gebruikt verschillende transistoren om te bouwen zijn comparatoren (Zie de opmerkingen van de afbeelding in fig 3), zodat in de vereenvoudigde Werkingsschema in fig 2 zij worden vertegenwoordigd door de vakken gelabelde "vergelijkingslocatie." De comparator aangesloten op pin 2 vergelijkt de "trigger" ingang met een referentie spanning van 1/3Vcc en de comparator verbonden in pin 6 vergelijkt de "drempel" input met een spanning van de verwijzing van 2/3Vcc van de scheidingslijn van de spanning.

Een flip flop is circuit dat wordt geschakeld tussen twee stabiele staten op basis van de status van haar ingangen. De 555 flip flop uitgangen een hoog of laag op basis van de Staten van de twee comparatoren. Wanneer de trigger comparator is het uitvoeren van een laag signaal (ongeacht de status van de drempel comparator), schakelt de flip flop hoog, bij beide comparatoren zijn uitvoer een hoog signaal, de lage flip flop-switches. De timing van de uitvoer van een hoge pols van de flip flop kunnen ook handmatig opnieuw instellen (het begin van een puls kan worden geactiveerd) door de resetpin pulserende laag.

De Werkingsschema in fig 2 bevat ook twee transistoren. De transistor gekoppeld aan pin 7 is een NPN-transistor. Aangezien pin 7 is aangesloten op de pin van de verzamelaar van de NPN-transistor, heet dit type configuratie open collector of open afvoer. Deze pin is meestal verbonden met een condensator en wordt gebruikt voor het verlenen van kwijting de condensator telkens die de uitgang-pins laag gaat. De transistor aangesloten op pin 4 is een PNP transistor. Het doel van deze transistor is de resetpin, buffer zodat de 555 niet source huidige van deze pin en daardoor verzakken in spanning.

De fase van de uitgang van de 555 timer wordt aangegeven in de afbeelding tonen van fig 3. Het doel is om op te treden als een buffer tussen de 555 timer en eventuele belastingen die aan de uitgang-pins kunnen worden verbonden. De output stadium levert huidige aan de uitgang-Pins, zodat de andere functionele component van de 555 timer niet moet.