Stap 5: logische Circuits

De circuits hier zullen heel simpel, maar vergt een groot aantal discrete N-ch en P-ch MOSFETs of logica ICs. Logica ICs zijn goedkoop en gemakkelijk te vinden (probeer deze link voor de IC 4001) of deze link voor de 7402 IC, die beide quad NOR-poorten, zodat het niet te moeilijk.

De circuits vandaan Forrest Mims boek digitale logica projecten: werkmap II. Hier is een link naar de PDF van RadioShack, of naar Amazon.com voor aankoop. (Als een terzijde, ik aanraden om basis elektronica: Transistors en geïntegreerde schakelingen: werkmap ik zo goed, ook van Forrest Mims. Amazon.com of PDF)

Sommige dingen om te onthouden wanneer u werkt met logica ICs:

- Zorg om te voorkomen dat een statische opbouw of kwijting om te voorkomen beschadiging van de chips.

- Elke chip heeft een gemeenschappelijke pin voor + V en een gemeenschappelijk GND pin. Deze worden niet weergegeven op het schema, maar moeten gemakkelijk te vinden in het gegevensblad (gegevensblad 7402).

- Elke input pinnen die niet worden gebruikt moeten worden aangesloten op GND. Dit zal ook niet worden getoond op de schema's.

- Logica chips zijn niet bedoeld als hoog recente stuurprogramma's voor grote belastingen als motoren en dergelijke. Maar ze kunnen worden gebruikt voor kleine lastdragers, zoals een LED of tot de verstrekking van het signaal voor dergelijke stuurprogramma's, zoals in stap 3

Noteer het nummer van de SN74XX boven elke poort voor de volgende schema's. Dat is het nummer van de IC dat ik gebruikt om te bouwen van de circuits als u wilt krijgen enkele Internet-verbinding delen en deze op uw eigen te bouwen. De meeste van deze chips is voorzien van 4 van de specifieke poort, zodat de SN7402 hieronder 4 NOR poorten hebben zou.

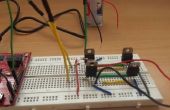

OK, laten we beginnen met een simpel LED flasher. Met behulp van slechts twee NOR gates, kunnen we bouwen een oscillator. Zie schema hieronder.

LED2 en R4 zijn optioneel als u wilt hebben twee LED's die flash heen en weer. Anders LED1 knippert aan/uit aan een tarief bepaald door de waarden van R1 (probeer een potentiometer hier) en C1.

Het volgende circuit is een set/reset-klink, die een essentieel onderdeel van de sequentiële logica. Hang de basis vormen van geheugen van de computer, aangezien de uitvoer blijft aan/uit, zelfs nadat u de schakeloptie loslaat. Een groep van 8 sloten vormt de kern structuur voor een 8-bits geheugencel. In het geheugen, de SR hendel staat bekend als een D klink (gegevens) en met de kern van de systeemklok wordt gebruikt om te bepalen wanneer om te haken. (Er is meer aan de hand, maar het valt buiten het bestek van deze I'ble. Kijk hier voor meer informatie over de werking van computergeheugen, en hier voor een vergelijking tussen sequentiële en de combinatorische logica.) Nu, het schema.

Dit circuit is meer een demonstratie van concept omdat we meestal alleen geïnteresseerd in een uitgang van de hendel zijn want als de uitgangen flip-flop tussen staten zoals de knoppen worden ingedrukt, ze zal altijd op tegenovergestelde Staten met elkaar zijn verbonden. U kunt binden een van de uitgangen hier naar een tweede circuit en gebruiken de klink als een "druk op / af duwen", niet-mechanische schakelaar voor het 2e circuit.

Zoals eerder vermeld, kan een logische poort of circuit worden gemaakt van een eindig aantal NAND-poorten. Hier is een voorbeeld van een OR poort met 3 NAND-poorten gemaakt.

De UPR's omzetten in een NOR, het toevoegen van een vierde NAND tussen de uitvoer van U3 en de LED, met samengebonden de twee ingangen van U4.

Het lijkt alsof het zou duurder om te gebruiken veel meer MOSFETs te doen van het zelfde ding (4 voor 1 NOR poort, 16 voor 3 NAND-poorten) en wanneer u ontwerpt een nieuwe chip, ruimte en het aantal onderdelen dat ruimte de belangrijkste zaak met betrekking tot de kosten van de chip is. Nou, is hier het voordeel. Onthoud de FPGA-chips die ik eerder al noemde? Dit zijn de algemene chips die kunnen worden geprogrammeerd voor elke situatie. Als we een enorme bin van NAND-poorten die kan om het even wat hebben, kunnen dan we.... Maar als we proberen te besparen van ruimte en kosten met behulp van specifieke poorten, we worden beperkt door het aantal elke poort die we hebben. Wat gebeurt er wanneer we meer OR poorten nodig? Klinkt als een redesign voor mij, en dat kost ook geld. Het punt is dat als u een specifiek ontwerp al in gedachten hebt, het wellicht beter om de exacte poort nodig en niet een opslaglocatie van generieke NAND-poorten te gebruiken. Maar bent u prototyping en ontwerpen vanaf nul, u flexibiliteit nodig hebt, en dat is waar NAND-poorten schitteren.

Maar goed, terug naar het. Opnieuw gebruikend slechts NAND gates, kunnen we bouwen een XNOR-poort.

Door het verwijderen van de U5 en koppelverkoop van de output van de U4 met R3, krijgen we een XOR poort.

Een enkele XOR poort kan worden gebruikt als een binaire adder van 1 bit. Door toevoeging van twee NAND-poorten (dat is gewoon een AND-poort als u herinneren), krijgen we een half-adder met een twee-bit output.

Een full-adder vereist een paar veranderingen (een XOR, twee NANDs en een OR poort toevoegen), die een ingang voor het afhandelen van carry-in in signalen van een vorige adder toe te voegen. Verschillende adders zijn een adder voor elke bit, om te bouwen van een machine toe te voegen dan samen, gestapeld. Het is eigenlijk vrij elegante. Hieronder is een volledig-adder-circuit.

PB1 bits A is, PB2 is beetje B en PB3 is de carry-bit van het vorige blok van de adder. Als we alleen druk op PB1 of PB2, we zijn het toevoegen van 1 + gaat 0 en enige LED 2 branden om aan te geven van een waarde van 1. Als we druk op PB1 en PB2 samen, betekent dit een binaire toevoeging van 1 + 1, oftewel 10 in binaire (aangegeven als 10b). Dat zal oplichten LED1 en LED2 weglaten. Als we vervolgens druk op PB3 en meer er 1 bij optellen, krijgen we 11b, en beide LEDs licht.

Hieronder is een blokdiagram voor een 4-bits adder gebruikend 4 volledig-adder blokken. Het eerste blok aan de rechterkant (met A0 en B0) kan worden verwisseld met een half-adder met geen effect op de uitgang. Het eenvoudig verwijdert de de carry-in (Cin) op de eerste full-adder, die is verbonden met GND hier toch.

In dit voorbeeld we zijn het toevoegen van twee, 4-bits getallen A en B. De eerste bits van elke (A0 en B0) worden toegevoegd aan de rechterkant, met het resultaat verzonden naar de S0 en eventuele carry bits (C1) verzonden naar het volgende adder. A1 en B1 worden vervolgens toegevoegd, samen met de C1 uit de eerste adder, het resultaat gaat naar uitgang S1, en elke bit dragen wordt verzonden op (C2). De laatste adder wordt weergegeven die de definitieve carry-out bit (C4), indien van toepassing, of genegeerd als er geen ruimte is of als het is onbelangrijk. U de ontwerper krijgen om die beslissing te nemen.

Laten we eens kijken naar een meer logica voorbeeld, een 4-bits Comparateur digitale lock. Zoals vermeld, XOR poorten kunnen worden gebruikt als adders, maar ze zijn ook comparatoren, outputten één staat als beide inputs zijn hetzelfde, en het omgekeerde staat als beide ingangen verschillend zijn. Hierdoor kunnen de status van een PIN-code controleren en schakelen en output alleen als het klopt.

De pinnen aangeduid 1, 2, 3, en 4 zijn voor het programmeren van de vergrendeling. U stelt deze pinnen hoog of laag om te bepalen van de combo, en dan heb je te druk op de dezelfde overeenkomstige knoppen PB1-PB4 om de uitvoer van U13 te laag gaan. Hierdoor huidige stroom door de LED en het blijkt op. Instellen van de combo u kunt ofwel binden de pinnen direct met GND of + V, of gebruik een soort memory device die slaat de input één keer instellen en niet wijzigen. Correcte huisvriend? Yep, kunt u gemakkelijk een klink circuit op de 4 combo set pinnen. Zolang de hang niet de stroom uitvalt, zullen ze niet verliezen de waarde die is opgeslagen in hen. De aanvragen voor deze zijn eenvoudig op zijn best, maar het idee krijgt over. (Ik ben op geen enkele wijze verantwoordelijk voor de manier waarop u wilt dit circuit moet worden gebruikt als het is niet echt veilig en kan gemakkelijk gehackt/reset.)