Stap 5: De code koppelen

Beschrijving van de code:

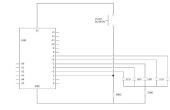

FSM1: Biedt de volgorde die een inschakelen signaal aan de FSM2 geven zal

FSM2: Een beetje teller die met één keer het verhogen zal ontvangt het signaal van de FSM1

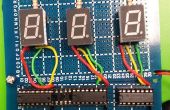

SSEG: De hersenen van de zeven segment display en die weer te gebruiken. Decodeert alle bits waarden die van het FSM geven.

clk_div: vertraagt de klok, zodat FSM2 niet te snel doet aanwas

Voor ons project, aangezien we een Basys 3 board gebruikten, zal moeten we onze code uploaden via het basys_master-bestand waarin de stap vóór. Het bestand basys_master zal laten te communiceren met elk hardwareonderdeel op het bord. In Verilog of uw IDE, door het basys_master-bestand te uploaden naar de beperkingen-bestand.

Basys_master: https://www.digilentinc.com/Products/Detail.cfm?N... (download aan de onderkant van de link) of gebruik ons met alle componenten van de gekoppelde bestuur

Als u vanuit naar de verbinding downloaden, is hier wat u wilt wijzigen in het bestand

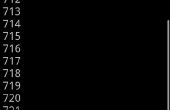

- uncomment de klok signaal gedeelte (regels 7-9)

- uncomment de sectie 7 segment display (lijnen 82-107)

- hoofdletters de seg -> SEG voor elk geval

- hoofdletters de een -> AN

- een van de knoppen uncomment (dit zal slechts twee lijnen, die uncommented worden zal)

- Onder JXADC, uncomment de eerste 2 pinnen (lijnen 208-213)

- Verandering van JXADC [0] -> PressureA en JXADC [1] -> PressureB

Nu alles is met elkaar in de code verbonden, is het tijd om het draad aan het bestuur en de test.