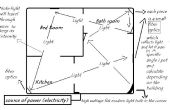

Stap 2: Board Modules

De acties worden uitgevoerd die worden beschreven in de vorige stap, nodig het FPGA-board meerdere modules die de noodzakelijke taken opeenvolgend uitgevoerd. Dit betekende dat de meeste van de modules hebben zou de dezelfde kloksignaal te delen en worden getimed, zodat ze in sync werken. Dit wordt gedaan door het koppelen van de inputs en outputs voor meerdere eindige staat machine modules. Dit betekende dat onze laatste uitvoering veel verschillend van onze eerste voorstelling was. Hieronder opgenomen zijn in detail beschrijvingen van wat elke module doet, evenals VHDL voorbeeldbestanden voor de modules, samen met enkele modules die zijn ontworpen voor het testen van de functionaliteit van het circuit.

CONTROLE

De controlemodule bepaalt de andere eindige statuscomputers op het bord. Hierdoor dat is alles goed getimede zodat geen oneindige lussen die verhinderen dat het circuit actief optreden. Dit gebeurt doordat de regelblok een signaal naar een andere module (de scanmodule), vertellen om iets te doen. Het regelblok wacht op een antwoord van andere module voordat u verdergaat. Het roept vervolgens de volgende module (de module zoeken) zodra zij een reactie ontvangt om de voortzetting van het proces. Vervolgens, afhankelijk van het succes van het FIND-blok, het besturingselement vervolgens beide verlaagt blokkeren of de spanning van de verwijzing van de comparatoren teruggezet. Dit zorgt ervoor dat de andere modules alleen een actie uitvoeren als het absoluut noodzakelijk is.

SCAN

De scanmodule is degene die in de sensorgegevens uit de externe sensoren scant. Het doet dit door het beheersen van het SEL-signaal dat wordt uitgevoerd naar de externe muxes, en door het beheersen van de interne DMFLOP-module met behulp van een nl en SEL signaal. De module wacht op een signaal van het blok van de controle, en de scan begint wanneer zij het ontvangt. Het gaat door alle geldige SEL waarden, en Hiermee schakelt u de DMFLOP module zodat het de waarden worden opgeslagen in een register. Zodra alle waarden zijn opgeslagen, wordt een signaal gedaan naar het regelblok.

ZOEKEN

De module zoeken zoekt een maximale sensor-waarde van de gescande gegevens van de sensor. Zodra het een signaal van het regelblok ontvangt, zoekt de zoek-module een waarde '1' in de sensor-waardes, waarmee wordt aangegeven dat de spanning van de sensor was hoger dan de spanning van de referentie voor dat specifieke sensor. Het output dan een 7-bits waarde die is gerelateerd aan de positie van de waarde '1' in de sensor gegevens-array. Als het een '1' wordt gevonden, wordt een succes teruggekeerd naar het regelblok. Als er geen ' 1's zijn gevonden in de gegevens, wordt een fout signaal teruggestuurd naar het regelblok.

DMFLOP

De DMFLOP module is een gespecialiseerde flip flop-register dat een nl en SEL invoer van de blok van de SCAN haalt. Het maakt gebruik van deze signalen naar demultiplex de inbreng van de externe muxes en ze opslaan in het register. Deze module is belangrijk, omdat beide de SCAN en vinden blokken nodig hebben voor het circuit om te werken.

MAIN

De MAIN module kapselt de modules van de controle-, SCAN-, zoek- en DMFLOP in één enkele module. Hierdoor worden de modules die allen ontvangen dezelfde kloksignaal en maakt het veel gemakkelijker om te integreren in andere circuits modules. De MAIN module vereist alleen een interne kloksignaal en de ingang van de externe comparatoren met 3-bits. De resultaten zijn het SEL-signaal en twee signalen van de plicht van de 7-bits voor de motor en verwijst naar spanning PWM-signalen.

REF

De REF module neemt output van de controlemodule om te bepalen wat de 7-bits plicht waarde van de spanning van de verwijzing PWM moet worden. Is het kundig verlagen de spanning of opnieuw instellen op de maximale spanning, afhankelijk van de output van de controlemodule.

PWM

Het PWM-module genereert een puls breedte gemoduleerde signaal die direct aan een van de uitgangen van de Raad van bestuur is output. De module neemt in een 7-bits plicht signaal waarmee het pulserend sproeien van de PWM-signaal. De frequentie van het PWM-signaal wordt bepaald door het kloksignaal geleverd aan de module. In deze module wordt gebruikt om de spanning van de verwijzing en de motor PWM-signalen te genereren.

CLK_DIV

De CLK_DIV module is een klok-verdeler. Het output een kloksignaal met een frequentie die gelijk is aan de input klokfrequentie gedeeld door een geheel getal. De integer-waarde kan worden gewijzigd door een waarde in de klok scheidingslijn vhdl-bestand te wijzigen. Een klok-verdeler is nodig voor de belangrijkste module kloksignaal, alsmede voor de motor PWM-module. Krediet voor het maken van de CLK_DIV module gaat naar Bryan Mealy.

TEST/MUX

De TEST- en MUX-modules zijn modules voor het circuit testen.