Stap 15: Implementeren Circuit 1 in Verilog HDL

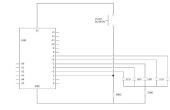

Bouwen en implementeren van logische vergelijking voor Circuit 1 volgens de waarheidstabel. Wij zal het construeren van de vergelijking van de logica in SOP vorm voor demonstratie. In Circuit 1, hebben wij twee rijen (tweede rij en derde rij) dat een "1" in de output toont. We moeten dus een OR poort met twee "inputs" die de output te genereren, en twee 2-input en poorten waarmee de input voor de OR-poort. In de tweede rij, ingang SW0 toont een "1" en input SW1 toont een "0". Dus SW0 is aangesloten op de ingang van de eerste en poort en SW1 is omgekeerd voordat u verbinding maakt met de tweede ingang van de AND poort, zoals aangegeven in het eerste semester van het product in de vergelijking. In de derde rij, ingang SW0 toont een "0" en input SW1 toont een "1". Dus SW0 is omgekeerd voordat u verbinding maakt met de ingang van de tweede en poort en SW1 rechtstreeks is aangesloten op de tweede ingang van de AND poort, zoals in de tweede termijn van het product in de vergelijking. De output LD0 is de sommatie van deze twee product voorwaarden.

Verilog HDL, wordt dit circuit uitgevoerd zoals hierboven.